On each successive positive clock edge, the 1 will “shift” to the next flip flop in the chain until it appears at the output of the shift register, which is the output of ff3 in the 4-bit shift register shown above. Result of two positive clock edges or "shifts" On the second positive clock edge, ff1 will capture a 1 because it has sampled the output of ff0 (see Figure 2):įigure 2. If all the flip flops start out reset to 0 and we hold the input of the shift register at 1, then a positive clock edge will cause ff0 to capture a 1. On a positive clock edge, ff0 will capture its input and ff1 will capture the current value of ff0. The input to ff1 is the output of ff0, which is also the current value of ff0. The input to ff0 is the input to the shift register. Consider the flip flops labeled 0 and 1 in Figure 1 (ff0 and ff1).

Let’s say we are using positive edge-triggered flip flops.

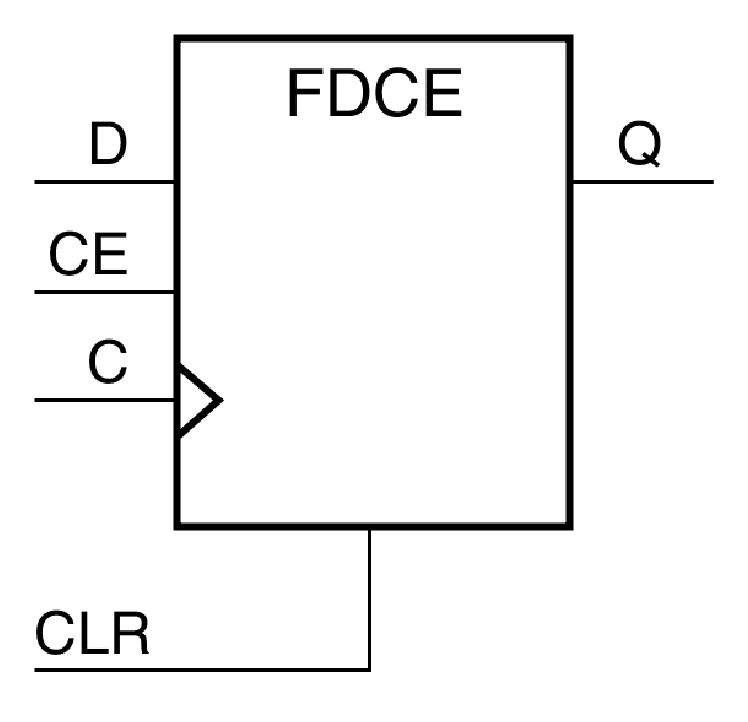

The storage elements are controlled by a common clock signal:

In its simplest form, a shift register consists of a number of storage elements (e.g., flip flops) connected in series, so that the output of one storage element feeds into the input of the next. Verilog Shift Register Basic Concepts/Characteristics

The register described can be synthesized and downloaded to an FPGA for test in actual hardware. This article will discuss how to implement a shift register in Verilog.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed